# Low-power CMOS Front-end ROIC using Inverter-feedback RGC TIA for 3-D Flash LADAR Sensor

Eun-Gyu Lee, Jae-Eun Lee, Han-Woong Choi, Kyeong-Hyeok Lee, Bang Chul Jung, and Choul-Young Kim

Abstract—This work proposes a pixel architecture for a front-end readout integrated circuit (ROIC) using an inverter-feedback regulated-cascode (RGC) transimpedance amplifier (TIA) for the focal plane array of a three-dimensional flash laser detection and ranging sensor. Although there are various TIA topologies for wideband operation, the inverterfeedback RGC structure is adopted owing to the importance of the small area and low power consumption of the array configuration. A single pixel also consists of an overcurrent protector, comparator, amplitude-to-voltage converter, and time-to-voltage converter to sense the range and intensity information of the remote object. A single pixel dissipates a power of 5.28 mW from a 3-V supply. The receiver achieves an input referred noise current of 7.5 pA/√Hz with a bandwidth of 453 MHz, transimpedance gain of 76  $dB \cdot \Omega$ , and a maximum detection range of 60 m with a 3.8-ns pulse. A single pixel is developed within 100 µm × 100 μm and the total die size, including the I/O pads, is 2200  $\mu$ m  $\times$  2200  $\mu$ m.

Index Terms—Laser detection and ranging (LADAR) sensor, readout IC (ROIC) array, optical receiver, flash LADAR, focal plane array

Manuscript received May. 17, 2017; accepted Nov. 12, 2017 Chungnam National University, Department of Electronic Engineering, Daejeon 34134, Korea

E-mail: cykim@cnu.ac.kr

#### I. Introduction

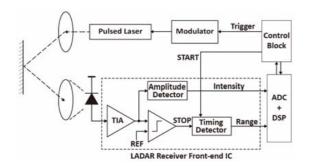

A laser detection and ranging (LADAR) sensor is an active imaging sensor that can acquire real-time threedimensional (3-D) imagery of targets by emitting and detecting laser pulses. It has been deployed in many applications such as reconnaissance, autonomous vehicles and robots, remote sensing, and surface mapping for buildings and scenes where high 3-D resolution is of prime importance [1-5]. For high-precision 3-D image acquisition, a pulsed time-of-flight (TOF) LADAR sensor is widely used to measure distances, compared with other measurement methods such as the continuouswave optical phase method [6, 7] or structured lightbased method [8]. Generally, a pulsed LADAR sensor consists of a laser transmitter, optical receiver, and signal processor module, as shown in Fig. 1. The outgoing laser pulse passes through the transmission optics, reflected from a target, and focused onto the photodetector through the receiver lens. The time between the launching of the pulse and its return is proportional to the range via the velocity of light. The receiver converts the detected optical signal into an electrical current pulse using a photodetector, converts the current into a voltage using a transimpedance amplifier (TIA), detects the pulse amplitude using an amplitude detector, produces a timed logic pulse (STOP) that indicates the arrival of the return signal using a comparator, and converts the TOF into a voltage using a timing detector.

There are various operation methods for the pulsed LADAR sensor with different scanning mechanisms,

Fig. 1. Block diagram of the typical pulsed LADAR sensor.

number of lasers, and geometric configurations [9-11]. In particular, a 3-D flash LADAR sensor can detect the 3-D image of an object moving very fast by measuring the TOF of the pulsed laser. A 3-D flash LADAR sensor obtains an entire frame of 3-D data by using a single-short laser pulse and a focal plane array (FPA) of photodetectors, along with its corresponding front-end readout integrated circuits (ROICs) [11]. There are many challenges in designing the ROIC. Especially, in an array configuration, extensive power management would be necessary to keep the power consumption to a reasonable level [12]. Additionally, the size of the circuits for the ROIC should be small enough to fit within the pixel dimension.

This paper focuses on the TIA for a low-power pixel implementation for the FPA. Among the various TIA topologies available for wideband operation, a pixel architecture using the inverter-feedback regulatedcascode (RGC) structure is proposed, owing to its low power consumption and small-area characteristics. The implemented ROIC consists of an overcurrent protection circuit (OCP), comparator, amplitude-to-voltage converter (A2V), and time-to-voltage converter (T2V). The ROIC for a unit pixel and its array are implemented in 0.18-µm CMOS technology for a flash LADAR sensor using avalanche photodiode (APD) detectors. The proposed pixel is developed within 100  $\mu$ m  $\times$  100  $\mu$ m for high resolution, and this pixel is expanded to a  $2 \times 8$ array. The amount of current consumed by a proposed unit pixel is approximately 1.76 mA.

# II. PROPOSED PIXEL ARCHITECTURE

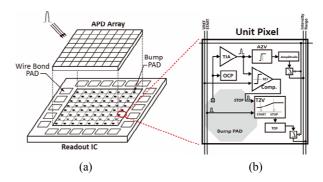

Fig. 2(a) is an illustration of the simplified 3-D FPA [11].

Each photodetector is connected to its corresponding

Fig. 2. Block diagram of the proposed transmitter.

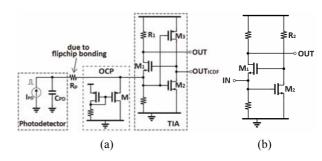

**Fig. 3.** Schematic of (a) implemented inverter-feedback RGC TIA with an OCP and photodetector model, (b) conventional RGC-TIA.

ROIC via a metal bump. The proposed pixel architecture is illustrated in Fig. 2(b). The unit pixel consists of five parts: TIA, OCP, comparator, A2V, and T2V. They should not consume much power in an array configuration, and the size of these components should be small enough to fit the pixel dimension.

First, the TIA, as a low-impedance input stage, amplifies the received photocurrent from a photodetector. The proposed pixel adopts an inverter-feedback RGC TIA, as shown in Fig. 3(a), rather than an inverter-type [13], shunt-feedback topology [14], C-TIA topology [15], or conventional RGC TIA [16]. Although the RCG structure has a slightly higher input-referred current noise than that in others, all other topologies, except the RGC structure, consume a large amount of current or occupy a large area. Hence, they are not considered. This work compares three different TIA structures intended for use in the pixel for a flash LADAR sensor. They are the inverter-feedback RGC TIA, an inverter based commondrain active feedback (ICDF) TIA [17], and conventional RGC TIA. The difference between the inverter-feedback TIA and ICDF TIA is the output node and the main amplifier or feedback stage. The inverter-feedback RGC output is taken from the drain of the common-gate

amplifier, as shown in Fig. 3(a), just as in the conventional RGC TIA, as shown in Fig. 3(b). The ICDF TIA output node is  $OUT_{ICDF}$ , which is the drain of the inverter amplifier in Fig. 3(a). The transimpedance gain of the inverter-feedback RGC TIA is the same as that of the conventional RGC-TIA and is given by:

$$Z_{T.INV-RGC} \cong R_1. \tag{1}$$

The transimpedance gain of the ICDF structure, where resistor  $R_1$  is replaced by a PMOS transistor  $M_3$ , is given by:

$$Z_{T,ICDF} \cong \frac{(r_{ds1} + R_1) \cdot A_{INV}}{1 + g_{m1} r_{ds1} (1 + A_{INV})}$$

$$\cong \frac{1 + R_1 / r_{ds1}}{g_{m1}} \quad \text{if } A_{INV} \gg 1,$$

(2)

where  $g_{m1}$  and  $r_{ds1}$  are the transconductance and output resistance of  $M_I$ , respectively, and  $A_{INV}$  is the voltage gain of the inverter stage. The transimpedance gain is determined by the ratio of  $1+R_1/r_{ds1}$  and  $g_{m1}$ .

The TIA bandwidth is limited by the parasitic parallel capacitance  $(C_{PD})$  owing to the large area of the photodetector and the parasitic series resistance  $(R_P)$  owing to flip-chip bonding, shown in Fig. 3(a). The small-signal input impedance of the inverter-feedback or ICDF structure is approximately given by (3)

$$Z_{in,INV-RGC} \approx \frac{1}{g_{m1} \left( 1 + A_{INV} \right)}$$

$$= \frac{1}{g_{m1} \left( 1 + \left( g_{m2} + g_{m3} \right) \left( r_{ds2} / / r_{ds3} \right) \right)}, \tag{3}$$

where  $g_{m1}$ ,  $g_{m2}$ , and  $g_{m3}$  are the transconductances of  $M_1$ ,  $M_2$ , and  $M_3$ , respectively.

The small-signal input impedance of the conventional RGC TIA, as shown in Fig. 3 (b), can be calculated from (4).

$$Z_{m,RGC} \cong \frac{1}{g_{m1} (1 + A_{CS})}$$

$$= \frac{1}{g_{m1} (1 + g_{m2} (R_2 / / r_{ds2}))},$$

(4)

Table 1. TIA Performance Comparison

|                                    | This work                                  | ICDF-RGC                                   | Conventional-<br>RGC                        |

|------------------------------------|--------------------------------------------|--------------------------------------------|---------------------------------------------|

| C <sub>PD</sub> [pF]               | 1                                          | 1                                          | 1                                           |

| Transimpedance gain [dB $\Omega$ ] | 76                                         | 61                                         | 76                                          |

| Bandwidth [MHz]                    | 453                                        | 456                                        | 420                                         |

| Input-referred noise [pA/√Hz]      | 7.5                                        | 12.3                                       | 7.7                                         |

| Current consumption [mW]           | 0.27                                       | 0.27                                       | 0.21                                        |

| Size of $M_3$ or $R_2$ (L/W)       | 1.9 μm<br>× 8 μm<br>(7.2 μm <sup>2</sup> ) | 0.9 μm<br>× 8 μm<br>(7.2 μm <sup>2</sup> ) | 8 μm<br>× 1.4 μm<br>(11.2 μm <sup>2</sup> ) |

where  $g_{m1}$  and  $g_{m2}$  are the transconductances of  $M_I$  and  $M_2$ , respectively. The input impedance of the inverter-feedback RGC TIA or ICDF TIA can be lower than that of the conventional RGC structure owing to the large voltage gain of the inverter stage.

The three TIA topologies are designed and simulated for performance comparison. Except the resistor  $R_2$  in Fig. 3(b), all other component values for the conventional RGC TIA are the same as those of the inverter-feedback TIA in Fig. 3(a). The simulation results are summarized in Table 1. The ICDF TIA has lower transimpedance gain and higher input-referred noise current than other topologies. The inverter-feedback RGC TIA and the conventional RGC TIA show similar simulation results. However, the size of  $R_2$  in the conventional RGC TIA is approximately 1.5 times larger than the size of  $M_3$  in the inverter-feedback RGC TIA. Moreover, in many CMOS technologies, the process variation of the resistor is larger than that in a MOS transistor. In order to minimize the inter-pixel variation in the array structure, the inverter-feedback RGC TIA using a MOS transistor instead of a resistor is selected.

The bandwidth required for the TIA to preserve its rise time, can be approximated from [6] as

$$BW \cong \frac{0.35}{t_{r}},\tag{5}$$

where  $t_r$  is the rise time of the input pulse. In this work, the full width at half maximum (FWHM) of the input pulse is approximately 3.8 ns and its rise time is approximately 1 ns. For a rise time of 1 ns, (5) gives a bandwidth of approximately 350 MHz. With a photodetector parasitic parallel capacitance  $C_{PD}$  of 1 pF

and parasitic series resistance  $R_P$  at 100  $\Omega$ , the simulated bandwidth of the designed TIA is approximately 453 MHz. The TIA achieves an input referred noise current of 7.5 pA/ $\sqrt{\rm Hz}$  with a bandwidth of 453 MHz and a transimpedance gain of 76 dB· $\Omega$ . The amount of current consumed by the TIA is approximately 0.27 mA per pixel.

The OCP, as shown in Fig. 3, is designed to protect the pixel from being damaged by the very high input photocurrent. [13]. Transistor M only turns on when its source voltage is greater than 1.7 V, and size of the transistor M is big enough to sink several milliamperes. When the input current is approximately 200  $\mu$ A, the source voltage of M reaches 1.7 V.

The remaining circuits in the pixel are conventional circuits that occupy a small area. The simplest way of defining the timing point is the leading-edge technique, in which the rising edge of the signal is compared with the constant threshold voltage [6]. A comparator produces a STOP signal, which is a timed logic pulse that indicates the arrival of the return signal. The comparator implemented in the pixel consists of a decision stage [18] and post-amplifier [19]. A2V detects the amplitude of the return pulse using a peak-detect-and-hold circuit (PDH) and sample-and-hold circuit (SH). The PDH used in this pixel was proposed by Kruiskamp and Leenaerts in 1994 [20, 21]. The SH is designed to be turned on for a short time at the falling edge of the comparator output pulse to the intensity information. Finally. save proportionally converts the time between START and STOP into a voltage [22]. The implemented T2V is able to measure time intervals over a linear range of 30 - 400ns, which corresponds to 60 m.

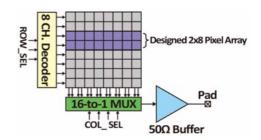

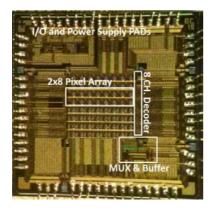

A functional diagram of the fabricated chip is shown in Fig. 4. The designed ROIC of 2  $\times$  8 pixels is placed in an 8  $\times$  8 pixel array. To read the stored intensity and range information in each pixel, an eight-channel decoder for row selection; a 16-to-1 multiplexer for column and output type, intensity, and range; and an output buffer of 50  $\Omega$  for output impedance matching are additionally designed.

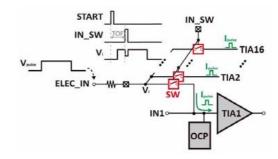

To characterize the designed ROIC array without a flip-chip bonded photodetector, it is impossible to induce the current pulse in every pixel via I/O pads. In this work, a switch is added to each input path, and all inputs of the switch are connected to a single node, as shown in Fig. 5.

Fig. 4. Functional diagram of fabricated chip.

**Fig. 5.** Operation principle of input path switch for array test with electrical current pulse.

A long voltage pulse is applied to ELEC\_IN. Once IN\_SW is shortly turned on, the current pulse with the same pulse width as IN\_SW is passed through the switch. This electrical current pulse is concurrently induced in every pixel with the same amplitude.

## III. MEASUREMENT RESULTS

The designed ROIC of 2  $\times$  8 pixels was fabricated using a standard 0.18- $\mu$ m CMOS process a microphotograph of the fabricated chip is shown in Fig. 6. The total chip size, including the I/O pads, is 2200  $\mu$ m  $\times$  2200  $\mu$ m, and the unit pixel occupies an area of 100  $\mu$ m  $\times$  100  $\mu$ m. All DC biases were connected to an external power supply through bonding wires.

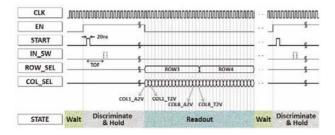

An example of the waveform of key signals involved in the designed pixel array is illustrated in Fig. 7. All signals are generated from an external control board with an FPGA. A global clock signal CLK modulated at a frequency of 40 MHz is used as a reference signal. The EN signal can be used as a trigger signal for the laser transmitter and measurement equipment. When EN is high, the pixel receives the input signal and stores the pulse intensity and range. In the discriminate-and-hold mode, the START and IN\_SW signals are enabled for a clock at intervals of TOF. The read operation starts when

Fig. 6. Functional diagram of fabricated chip.

Fig. 7. Sensor timing diagram.

EN is low. In the readout operation, the selection of 32 outputs can be accomplished with ROW\_SEL for row selection and COL\_SEL for a 16:1 data mux, which is for the readout of stored data in each pixel through an output pad. For each pixel, the peak amplitude from A2V and the range information from T2V are selected by turns.

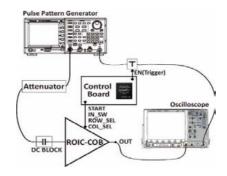

To facilitate the measurement of the electrical pulse response, the fabricated chip was mounted on an FR-4 PCB test fixture. The measurement setup is described in Fig. 8. A long electrical pulse, generated from a function generator, was applied to ELEC\_IN of the implemented test fixture. The OUT signal was measured by using an Agilent DSO7104B oscilloscope. To control the operation of the fabricated array circuit, an external control board with an FPGA was implemented. It generates EN, START, IN\_SW, ROW\_SEL, and COL\_SEL from a global clock signal CLK.

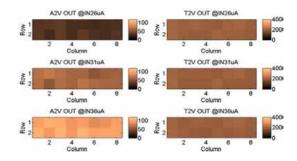

Fig. 9 shows the measured A2V and T2V outputs corresponding to an input current of 26, 31, and 36  $\mu$ A with a TOF of 100 ns. The A2V output increases with the input current, but the T2V output is the value for a TOF of 100 ns. By contrast, Fig. 10 shows the measured output voltages corresponding to a TOF of 60, 80, 100, and 200 ns with an input current of 26  $\mu$ A. The T2V output increases with the TOF but the A2V output

Fig. 8. Measurement setup for electrical pulse test.

Fig. 9. Measured intensity and range map vs. input current amplitude.

Fig. 10. Measured intensity and range map vs. TOF.

maintains the level for an input current of  $26 \mu A$ . From these results, the designed array ROIC is able to generate 3-D images according to the intensity and TOF of the return pulse, and it has the potential to be scaled to a larger FPA using the designed pixel.

A single pixel dissipates a power of 5.28 mW. The total power consumption for  $2 \times 8$  pixels, including 54 mW of the output buffer for 50- $\Omega$  impedance matching, is 138.5 mW from a 3-V supply.

Table 2 gives a performance summary of the proposed LADAR sensor in comparison with recently published works. It is clear from the table that a significant improvement is achieved in the power consumption, with

|                               | This work        | [5]               | [13]               | [15]            |

|-------------------------------|------------------|-------------------|--------------------|-----------------|

| Array                         | 2 × 8            | 1                 | 1                  | 1               |

| C <sub>PD</sub> [pF]          | 1                | 1.5               | 2                  | 2.5-5           |

| Transimpedance gain [dBΩ]     | 76               | 81                | 78                 | 80              |

| Bandwidth [MHz]               | 453              | 230               | 640                | 160             |

| Input-referred rms noise [µA] | 0.16             | 0.05              | 0.12               | 0.02            |

| Power consumption [mW]        | 5.28*            | 115               | 114                | 79              |

| Chip size [mm <sup>2</sup> ]  | $2.2 \times 2.2$ | 1.85 × 1.85       | $0.89 \times 0.66$ | 1.2 × 1.2       |

| Technology                    | CMOS<br>0.18 μm  | BiCMOS<br>0.35 μm | CMOS<br>0.13 µm    | CMOS<br>0.35 μm |

Table 2. Receiver Performance Comparison

an acceptable bandwidth of 453 MHz.

## V. CONCLUSIONS

An integrated, wideband, and low-power ROIC for unit pixels, intended for use in a 3-D flash LADAR sensor, and its  $2 \times 8$  array were designed, implemented, and tested with an electrical current pulse in the present work. The measurement results confirmed that the operation of the array ROIC is in accordance with the working principle of the FPA for a flash LADAR sensor.

#### ACKNOWLEDGMENTS

This work was supported in part by the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Science and ICT (NRF-2015R1C1A1A01052508) and in part by the Basic Science Research Program through the NRF funded by the Ministry of Science and ICT (NRF-2016R1A2B4014834).

# REFERENCES

- [1] S. Thrun, M. Montemerlo, H. Dahlkamp, D. Stavens, A. Aron, J. Diebel, P. Fong, J. Gale, M. Halpenny, G. Hoffmann, K. Lau, C. Oakley, M. Palatucci, V. Pratt, and P. Stang, "Stanley: the robot that won the DARPA grand challenge," *J. Field Robot.*, 23 (9), pp. 661–692, Sep. 2006.

- [2] C. Wang and N. F. Glenn, "Integrating LIDAR intensity and elevation data for terrain characterization in a forested area," *IEEE Geosci.*

- Remote Sens. Lett., vol. 6, no. 3, pp. 463–466, Jul. 2009.

- [3] G. Buller and A. Wallace, "Ranging and three-dimensional imaging using time-correlated single-photon counting and point-by-point acquisition," *IEEE J. Sel. Topics Quantum Electron.*, vol. 13, no. 4, pp.1006–1015, Jul.–Aug. 2007.

- [4] W. E. Hong, J.-S. Lee, L. Rai, and S. J. Kang, "Embedded Real-Time Software Architecture for Unmanned Autonomous Helicopters," *Journal of Semiconductor Technology and Science*, vol. 5, no. 4, pp. 243-248, Dec. 2005.

- [5] S. Kurtti and J. Kostamovaara, "An integrated laser radar receiver channel utilizing a time-domain walk error compensation scheme," *IEEE Trans. Instrum. Meas.*, vol. 60, no. 1, pp. 146–157, Jan. 2011.

- [6] T. Ruotsalaine, P. Palojärvi, and J. Kostamovaara, "A wide dynamic range receiver channel for a pulsed time-of-flight laser radar," *IEEE J. Solid-State Circuits*, vol. 36, no. 8, pp. 1228-1238, Aug. 2001.

- [7] J. Pehkonen, P. Palojärvi, and J. Kostamovaara, "Receiver channel with resonance-based timing detection for a laser range finder," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 53, no. 3, pp. 569-577, Mar. 2006.

- [8] B.-J. Hong, C.-O. Park, N.-S. Seo, and J.-D. Cho, "A Real-time Compact Structured-light based Range Sensing System," *Journal of Semiconductor Technology and Science*, vol. 12, no. 2, pp. 193-202, Jun. 2012.

- [9] Glennie, C., and Lichti, D.D.: "Static calibration and analysis of the velodyne HDL-64E S2 for high accuracy mobile scanning," *Remote Sens.*, 2, pp. 1610–1624, 2010.

- [10] E. G. Lee, J. An, and C. Y. Kim, "A fully integrated four-input combining receiver front-end circuit for laser radar with static unitary detector," *Electron. Lett.*, vol. 50, no. 21, pp. 1543–1545, Oct. 2014.

- [11] R. Stettner, H. Bailey, and S. Silverman, "Three dimensional Flash LADAR focal planes and time dependent imaging," *Int. J. High Speed Electron. Syst.*, vol. 18, iss. 2, pp. 401–406, Jun. 2008.

- [12] M. Browder et al., "Three-Dimensional Imaging Sensors program," Proc. SPIE4377, Laser Radar Technology and Applications VI, Sep. 2001.

- [13] T.-H. Ngo, C.-H. Kim, Y. J. Kwon, J. S. Ko, D.-B. Kim, and H.-H. Park, "Wideband receiver for a three-dimensional ranging LADAR system," *IEEE Trans. Circuits Syst. I: Reg. Papers*, vol. 60, no. 2, pp. 448-456, Feb. 2013.

- [14] A. Trabelsi and M. Boukadoum, "Comparison of Two CMOS Front-End Transimpedance Amplifires for Optical Biosensors," *IEEE Sensors J.*, Vol. 13, No. 2, pp. 657-663, Feb. 2013.

- [15] H.-S. Cho, C.-H. Kim and S.-G. Lee, "A High-Sensitivity and Low-Walk Error LADAR Receiver for Military Application," *IEEE Trans. Circuits Syst. I: Reg. Papers*, vol. 61, no. 10, pp. 3007-3015, Oct. 2014.

- [16] S. M. Park and H. Yoo, "1.25-Gb/s regulated cascode CMOS transimpedance amplifier for gigabit ethernet applications," *IEEE J. Solid-State Circuits*, vol. 39, no. 1, pp. 112-121, Jan. 2004.

- [17] M. Atef and H. Zimmermann, "10Gbit/s 2mW Inductorless Transimpedance Amplifier," *Proc. ISCAS*, Seoul, Korea, 2012, pp. 1728-1731.

- [18] A. Kapadia and V. Savani, "Analysis and Characterization of Different Comparator Topologies," *Int. J. Scientific and Technology Research*, vol. 1, iss. 11, pp.102-106, Dec. 2012.

- [19] R. Garipelly, "High Speed CMOS Comparator Design with 5mV Resolution," *Int. J. Engineering Trends and Technology*, vol. 4, iss. 4, pp.621-625, Apr. 2013.

- [20] M. W. Kruiskamp and D. M. W. Leenaerts, "A CMOS peak detect sample and hold circuit," *IEEE Trans. Nucl. Sci.*, vol. 41, iss. 1, pp. 295-298, Feb. 1994.

- [21] G.D. Geronimo, P. O'Connor, and A. Kandasamy, "Analog CMOS peak detect and hold circuits. Part 1. Analysis of the classical configuration," *Nuclear Instruments and Methods in Physics Research Section A*, vol. 484, pp.533-543, May 2002.

- [22] A. E. Stevens, R. P. Van Berg, J. Van der Spiegel, H. H. Williams, "A Time-to-Voltage Converter and Analog Memory for Colliding Beam Detectors,", *IEEE J. Solid-State Circuits*, vol. 24, no. 6, pp. 1748-1752, Dec. 1989.

**Eun-Gyu Lee** received the B.S. degree in electronics engineering from Chungnam National University (CNU), Daejeon, Korea, in 2004 and M.S. degrees in electrical engineering from Pohang University of Science and Technology (Postech),

Pohang, Korea, in 2006. She is working on her Ph.D. degree in electronics engineering in CNU. Her research interests include readout integrated circuits and systems for laser radar applications.

Jae-Eun Lee received the B.S. degree in electronics engineering from Chungnam National University (CNU), Daejeon, Korea, in 2006. He is working on his M.S. degree in electronics engineering in CNU. His research interests include readout

integrated circuits and systems for laser radar applications.

Han-Woong Choi received the B.S. degree in electronics engineering from Chungnam National University (CNU), Daejeon, Korea, in 2017. He is working on his M.S. degree in electronics engineering in CNU. His research interests include readout

integrated circuits and systems for phased-array antenna applications.

**Kyeong-Hyeok Lee** received the B.S. degree in electronics engineering from Chungnam National University (CNU), Daejeon, Korea, in 2017. He is working on his M.S. degree in electronics engineering in CNU. His research interests include readout

integrated circuits and systems for phased-array antenna applications

Bang Chul Jung received the B.S. degree in electronics engineering from Ajou University, Suwon, South Korea, in 2002, and the M.S. and Ph.D. degrees in electrical and computer engineering from Korea Advanced Institute of Science and

Technology (KAIST), Daejeon, South Korea, in 2004 and 2008, respectively. He was a Senior Researcher/ Research Professor with KAIST Institute for Information Technology Convergence, Daejeon, South Korea, from 2009 to 2010. From 2010 to 2015, he was a Faculty member with Gyeongsang National University. He is currently an Associate Professor of the Department of Electronics Engineering, Chungnam National University, Daejeon. His research interests include 5G mobile communication systems, statistical signal processing, opportunistic communications, compressed sensing, management, interference interference alignment, random access, relaying techniques, device-to-device networks, in-network computation, and network coding. Dr. Jung was a recipient of the Fifth IEEE Communication Society Asia-Pacific Outstanding Young Researcher Award in 2011. He also received the Haedong Young Scholar Award in 2015, which is sponsored by the Haedong Foundation and given by Korea Institute of Communications and Information Science.

Choul-Young Kim received the B.S. degree in electrical engineering from Chungnam National University (CNU), Daejeon, Korea, in 2002 and M.S. and Ph.D degrees in electrical engineering from Korea Advanced Institute of Science and Technology

(KAIST), Daejeon, Korea, in 2004 and 2008, respectively. From March 2009 to February 2011, he was a Postdoctoral Research Fellow at the department of electrical and computer engineering at the University of California, San Diego (UCSD). He is associate professor of electronics engineering at Chungnam National University, Daejeon, Korea. His research interests include mm-wave integrated circuits and systems for short range radar, phased-array antenna applications and readout integrated circuits for laser radar receiver.